### **EE330 HW3 Solutions**

### Problem 5

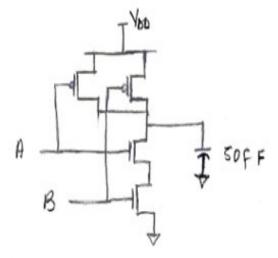

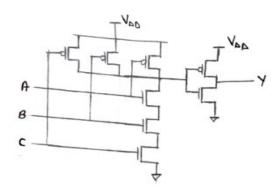

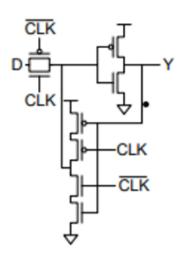

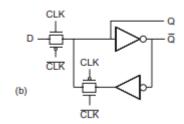

We can see that the figure of 1.31b) has 2 not gates and 2 T-gates.

**Problem 7**

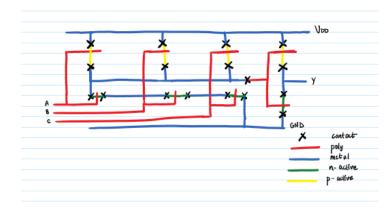

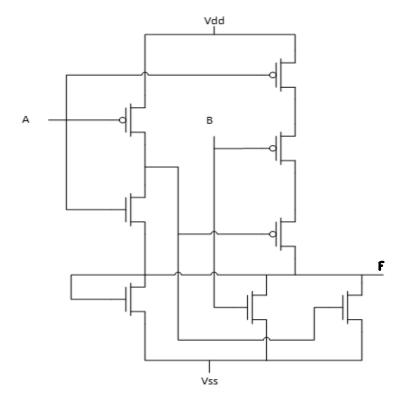

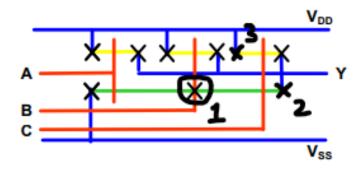

For this stick diagram there are 3 errors:

- 1. No need of contact poly to n-active.

- 2. Contact needed for Metal 1 to n-active.

- 3. Contact needed for Metal 1 to p-active.

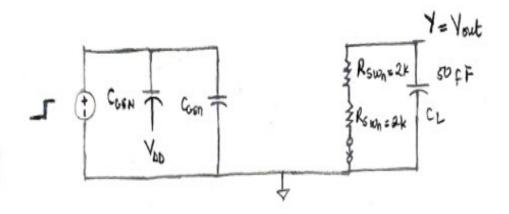

Assuming ON 0.18 $\mu$ m process,  $C_{IN}=1.5fF$ ,  $R_{SWP}=6k\Omega$ , and  $R_{SWN}=2k\Omega$  Total  $C_{IN}$  of 6 driven inverters =  $C_{IN}$  \* 6 inverters \* 2 transistors/inverter = 18fF =  $C_L$  If input steps from 2V to 0V, the transition at output will be from 0V to 2V, so we will be calculating  $t_{LH}$

From lecture,  $t_{LH} = C_L * R_{SWP} = 18 fF * 6 k\Omega = 108$  picoseconds

#### Problem 9

For this problem, there are three concepts to keep in mind

- Any interconnect will act as a resistor

- Conductivity is the inverse of resistivity

- Interconnect area =  $5\mu m * 0.2\mu m = 1\mu m^2$

Resistance =

$$\frac{\rho L}{A}$$

Resistance of first segment =  $\frac{\frac{1}{38}*(180+40)}{1} = \frac{220}{38} = 5.7895 \ ohms$

Resistance of second segment =  $\frac{\frac{1}{38}*(80)}{1} = \frac{80}{38} = 2.1053 \ ohms$

The voltage across the resistor =  $2V * \frac{50 \ ohms}{(50+5.7895+2.1053) ohms} = 1.727V$

The voltage across the resistor  $= 2V^{-\pi}$  (50+5.7895+2.1053) ohms b) Resistivity of copper  $= \frac{1}{58} \frac{ohm}{um}$

Resistance =

$$\frac{\rho L}{A}$$

Resistance of first segment =

$$\frac{\frac{1}{58}*(180+40)}{1} = \frac{220}{58} = 3.7931 \text{ ohms}$$

Resistance of second segment =  $\frac{\frac{1}{58}*(80)}{1} = \frac{80}{58} = 1.3793 \text{ ohms}$

The voltage across the resistor =

$$2V * \frac{50 \text{ ohms}}{(50+3.7931+1.3793)\text{ohms}} = 1.813V$$

```

/*structural implementation of f=(!a*b*c)+(a*b*!c)

EE330 - Integrated Electronics/

`timescale 1 \text{ns}/1 \text{ps}

//set timescale to something nice for simulation

module hw3q10(A, B, C, F);

//define module and IO

input A, B, C;

//define A, B, and C as inputs

output F;

//define F as an output

wire and1, and2;

//define intermediary wires to be used

and(and1, ~A, B, C);

//and1 = A!*B*C

and (and 2, A, B, \sim C);

//and2 = A*B*!C

or(F, and1, and2);

//F = and1 + and2 = (A!*B*C) + (A+B+!C)

endmodule

//end the module

/*behavioral implementation of f=(!a*b*c)+(a*b*!c)

EE330 - Integrated Electronics/

`timescale 1 ns/1 ps

//set timescale to something nice for simulation

module hw3q10(A, B, C, f);

//define module and IO

input A, B, C;

//define A, B, and C as inputs

output F;

//define F as an output

//define an output register for used

reg out;

assign F = out;

//assign output register to given output

always @ (A or B or C) begin

//when inputs change, execute the following

out = (\sim A\&B\&C) + (A\&B\&\sim C);

//f = (!A*B*C) + (A*B*!C)

//end of preceding always block

end

endmodule

//end the module

/*standard 3-input logic testbench

EE330 - Integrated Electronics

Nickolas Moser

February 2, 2022*/

`timescale 1ns/1ps

//set timescale to something nice to simulate

module standard tb();

//instantiate testbench module

```